CPEN 311: Multi-Core RC4 Cracking Circuit

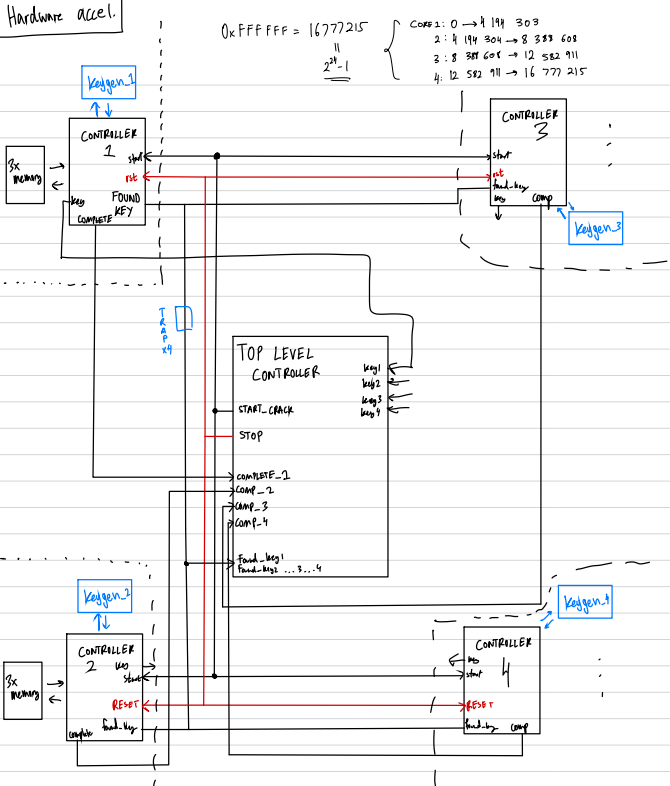

Lab 4 implements a hardware-accelerated RC4 cryptographic algorithm targeting key discovery through parallel brute-force processing. This lab demonstrates advanced FPGA design principles including multi-core architecture, efficient resource utilization, and cryptographic hardware implementation.

Key Accomplishments:

- Implemented RC4 stream cipher algorithm in VHDL with complete key scheduling algorithm (KSA) and pseudo-random generation algorithm (PRGA) stages

- Designed multi-core architecture enabling simultaneous testing of multiple key candidates in parallel

- Optimized hardware for maximum throughput by efficiently pipelining RC4 pipeline stages across FPGA resources

- Achieved significant performance gains over software implementations through hardware parallelization

- Created control logic for managing multiple RC4 cores and data flow synchronization

- Validated implementation through hardware testing and performance analysis

Technical Implementation:

The design employs multiple independent RC4 cores operating in parallel, each performing the complete cipher computation on different key candidates. This architecture leverages the massive parallelism available on FPGAs to achieve throughputs impossible with sequential software. The key scheduling algorithm initializes the RC4 state arrays, while the PRGA stage generates pseudo-random output for keystream comparison.

This project demonstrates deep expertise in cryptographic hardware design, parallel processing architectures, resource optimization for spatial computing, and security engineering. The parallel RC4 implementation showcases the capability to map compute-intensive algorithms to hardware for significant performance acceleration.