CPEN 311: FPGA iPod

Lab 2-3 is a progressive design project implementing a complete FPGA-based audio player system, advancing from Lab 2's foundation to Lab 3's optimized "pico" implementation. This comprehensive project integrates digital audio processing, user interface controls, and storage management into a functional music player.

Key Accomplishments:

- Designed audio codec interface modules for multi-bit audio signal handling and conditioning

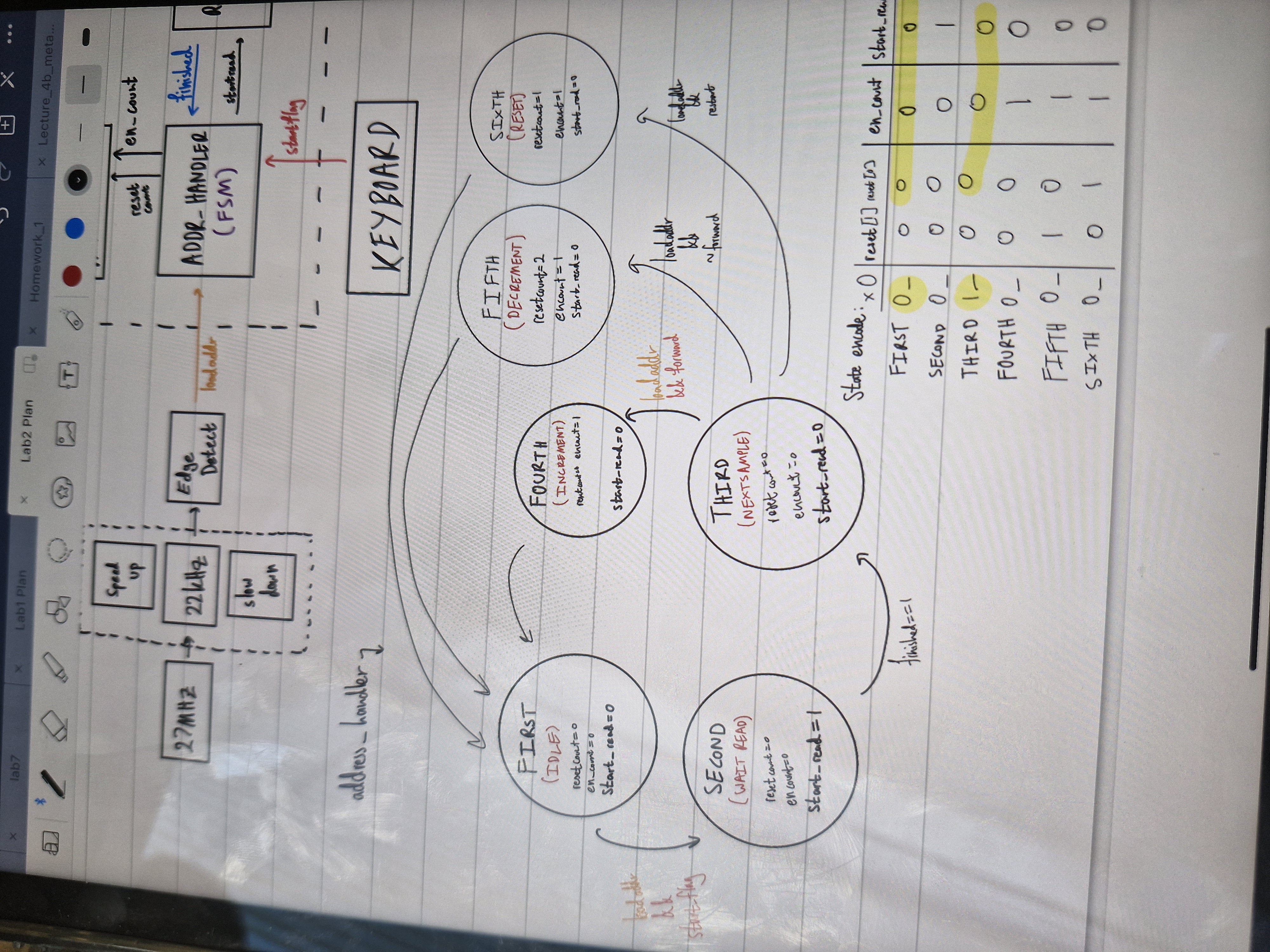

- Implemented user input/control logic with button debouncing and state machine management

- Created track selection and playlist management hardware with memory interfaces

- Developed SystemVerilog modules for audio buffering and real-time data streaming

- Implemented assembly language firmware for efficient device driver control

- Optimized design in Lab 3 (pico) version for reduced resource utilization while maintaining functionality

- Integrated all components into working audio playback system

Technical Implementation:

The system combines digital audio processing hardware modules with real-time control firmware. The audio codec interface handles clock domain crossing and signal timing requirements for high-fidelity audio. User controls employ debouncing logic to manage button inputs reliably, while state machines orchestrate track navigation and playback control. The "pico" optimization variant demonstrates resource-conscious design practices while preserving all functional requirements.

This multi-lab progression demonstrates mastery of: hardware-software integration, real-time embedded systems, digital signal processing fundamentals, user interface design, and FPGA resource optimization. The evolution from Lab 2 to Lab 3 showcases practical design iteration and optimization methodologies essential for engineering professional-grade embedded systems.